本文目的是要理清ARM处理器的CPSR状态标志和ARM指令的条件符之间的关系。

一、CPSR寄存器

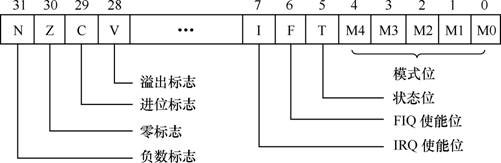

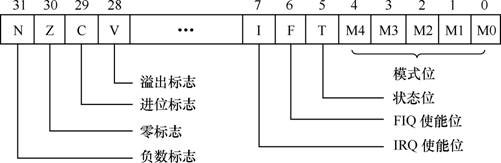

ARM V4的CPSR寄存器(和保存它的SPSR寄存器)中的位分配如下图1所示。

图1 程序状态寄存器格式

状态标志位含义:(其它位的含义和本文主题无关,此处不多介绍)

N

N=1 表示运算的结果为负数;N=0 表示运算的结果为正数或零;

Z

Z=1 表示运算的结果为零;Z=0表示运算的结果为非零;

C

可以有4种方法设置C的值:

─ 加法运算(包括比较指令CMN):当运算结果产生了进位时(无符号数溢出),C=1,否则C=0。

─ 减法运算(包括比较指令CMP):当运算时产生了借位,C=0,否则C=1。

─ 对于包含移位操作的非加/减运算指令,C为移出值的最后一位。

─ 对于其他的非加/减运算指令,C的值通常不改变。

V

可以有2种方法设置V的值:

─ 对于加/减法运算指令,当操作数和运算结果为二进制的补码表示的带符号数时,V=1表示符号位溢出。

─ 对于其他的非加/减运算指令,V的值通常不改变

二、条件符及对应的标志位

表1 条件符描述表

三、关于C、V值更多的解释

处理器内部以补码表示有符号数,8个二制位能够表达的整数范围是:+127 ~ -128,16位表达的范围是:+32767 ~ -32768。如果运算结果超出了这个范围,就是产生了溢出,有溢出,说明有符号数的运算结果需要考虑溢出情况。

溢出标志V和进位标志C是两个意义不同的标志。进位标志表示无符号数运算结果是否超出范围;溢出标志表示有符号数运算结果是否超出范围。

处理器对两个操作数进行运算时,按照无符号数求得结果,并相应设置进位标志C;同时,根据是否超出有符号数的范围设置溢出标志V。

应该利用哪个标志,则由程序员来决定。也就是说,如果将参加运算的操作数认为是无符号数,就应该关心进位;认为是有符号数,则要注意是否溢出。

判断运算结果是否溢出有一个简单的规则:只有当两个相同符号数相加,而运算结果的符号与原数据符号相反时,产生溢出;其他情况下,则不会产生溢出。

代码举例1:

LDRr0, =0x7fffffff

LDRr1, =0x70000000;

ADDSr0, r0, r1; //结果=0xefffffff

对于无符号数运算来说,没有进位。

对于有符号数运算来说,溢出。

此时C=0 V=1;

代码举例2:

LDRr0, =0xffffffff

LDRr1, =0x70000000;

ADDSr0, r0, r1; //结果=0x6fffffff

对于无符号数运算来说,有进位。

对于有符号数运算来说,无溢出。

此时C=1 V=0;

代码举例3:

LDRr0, =0x8fffffff

LDRr1, =0xf0000000 ;

ADDSr0, r0, r1; //结果=0x7fffffff

此时C=? V=?;(思考一下,然后在ARM模拟器中验证下)

代码举例4://思考减法时,C值的影响

LDRr0, =0x3

LDRr1, =0x2

SUBSr0, r0, r1

对比:

LDRr0, =0x3

LDRr1, =-2;(-2的补码0xfffffffe会送到r1)

ADDSr0, r0, r1

四、CPSR状态标志和ARM指令的条件符之间的关系

有了上面的背景知识以后,接下来思考表1中CPSR状态标志和ARM指令的条件符之间的关系,下面选取其中的一项来分析。

如:GE:(有符号数大于等于)

N=0 V=0:结果是大于等于0的数,且无符合溢出,所以大于等于关系成立

N=1 V=1:结果小于0,但有符号溢出

考虑以下情况:c=a-b

1.a<0, b<0

减法操作时不可能符号溢出

2.a>0, b<0

可能出现N=V=1?? 如(8位数):100-(-100)=200

显然a>b

3.a<0, b>0

参照上面提到过的判断溢出标志的简单规则,可以得出:在此情况下,

减法操作时如果结果小于0 (N=1),则不会出现符号溢出

所以(在N=1 V=1前提下a<0,b>0)这种情况不可能出现

4.a>0, b>0

减法操作不可能出现符号溢出。

其它项的分析过程类似。

五、总结

尽管以上分析看起来有点复杂,但使用时在大多数情况下用一个简单的条件测试指令即可,不需要程序员计算出条件码的精确值即可得到需要的结果。(作者:刘洪涛,华清远见嵌入式学院讲师。)

分享到:

相关推荐

本文目的是要理清ARM处理器的CPSR状态标志和ARM指令的条件符之间的关系。 一、CPSR寄存器 ARM V4的CPSR寄存器(和保存它的SPSR寄存器)中的位分配如下图1所示。 图1 程序状态寄存器格式 状态标志位...

ARM_cpsr寄存器

ARM CPSR + SPSR详解 1、SPSR 为 CPSR 中断时刻的副本,退出中断后,将SPSR中数据恢复到CPSR中。 2、用户模式和系统模式下SPSR不可用。

ARM中通过cpsr技术,可以让arm工作在不同的工作状态。

ARM中的程序状态寄存器(CPSR).pdf

当异常发生时,ARM处理器尽可能完成当前指令(除了复位异常)后,再去处理异常。并执行如下动作: 1. 进入与特定的异常相应的操作模式。 2. 将引起异常指令的下一条指令的地址保存到新模式的r14中。 3. 将...

当异常发生时,ARM处理器尽可能完成当前指令(除了复位异常)后,再去处理异常。并执行如下动作: 1. 进入与特定的异常相应的操作模式。 2. 将引起异常指令的下一条指令的地址保存到新模式的r14中。 3. 将...

一旦遇到一个 B 指令,ARM 处理器将立即跳转到给定的目标地址,从那里继续执行。注意存储在跳转指令中的实际值是相对当前 PC 值的一个偏移量,而不是一个绝对地址,它的值由汇编器来计算(参考寻址方式中的相对寻址...

THUMB指令集在功能上只是ARM指令集的一个子集,某些功能只能在ARM状态下执行,如CPSR和协处理器的访问. 进行异常响应时,处理器会自动进入ARM状态. 即使是一个单纯的THUMB应用系统,必须加一个汇编的交互头程序,因为系统...

cpsr

ARM 体系结构所支持的异常和具体含义如下: 1、复位(优先级1) ... 当处理器的外部中断请求引脚有效,且CPSR 中的I 位为0 时,产生IRQ 异常。系统的外设能该异常请求中断服务(异常向量:0x0000,0018);

ARM处理器核包含一个CPSR寄存器,该寄存器包括一个全局中断禁止位,控制它打开和关闭中断。 (4)处理器支持一定数量的数据存储硬件堆栈 对于一些只有10根地址线的8位控制器,芯片最多可访问1KB存储单元,在...

ARM可以用两套指令集:ARM指令集和Thumb指令集。本文介绍ARM指令集。在介绍ARM指令集之前,先介绍指令的格式。 1 指令格式 (1)基本格式 <opcode>{<cond>}{S} ,<Rn>{,<opcode2>} 其中,内的项是必须的,{}内的项...

SimIt-ARM-3.0 给予命令行ARM指令模拟器,短小精悍,是研究ARM处理器的好工具,该模拟器既可以运行用户级别的ELF程序,又可以模拟运行Linux操作系统;提供了简单易用的调试命令,可以逐条跟踪指令的执行。 SimIt-...

中断与堆栈设置和ARM体系结构紧密相关,ARM是一种支持多任务操作的系统内核,内部结构完全适应多任务应用。ARM内核支持7种中断,不同的中断处于不同的处理模式(如表1所示),具有不同的优先级,而且每个中断都有...

②尽量避免过早将处理器切换到用户模式,一般在系统初始化的最后阶段才切换到用户模式(用户模式没有权限通过修改CPSR来进行模式切换)。 嵌入式系统的迅猛发展,使启动代码的编写成为嵌入式系统开发人员应该具备...

它作为IP核、独立的处理器、具有片上高速缓存、MMU和写缓冲的集成CPU。变种版本有3G和3M。版本3G是不与版本2a向前兼容的版本3,版本3M引入了有符号和无符号数乘法和乘加指令,这些指令产生全部64位结果。V3版架构( ...

对初学arm的时,一些疑难问题进行总结,ARM汇编% ldr和adr CPSR_cxsf ^的作用 MACRO-MEND

A:经典ARM处理器包括Cortex-M、Cortex-R和Cortex-A三大类 B:Cortex-A系列为应用Cortex处理器,主要面向高端应用设计 C:Cortex-M系列为面向控制领域的实时嵌入式处理器 D:ARM11性能优于Cortex-A5,但低于Cortex-A15 12...

7.1 The Thumb bit in the CPSR 189 7.2 The Thumb programmer's model 190 7.3 Thumb branch instructions 191 7.4 Thumb software interrupt instruction 194 7.5 Thumb data processing instructions 195 7.6 ...